我國首個覆蓋計算機軟硬件基礎體系的綜合性標準正式發布,這一里程碑事件標志著我國在信息技術領域自主創新邁出了關鍵一步,對提升國家信息安全、推動產業升級具有重要意義。

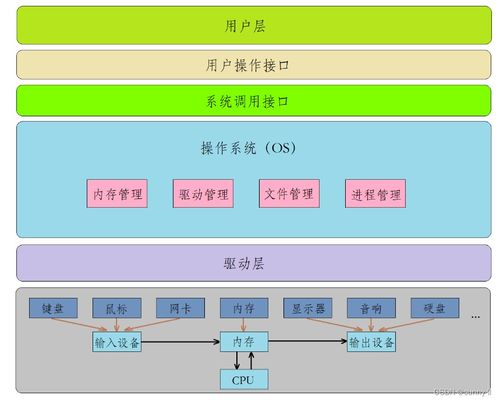

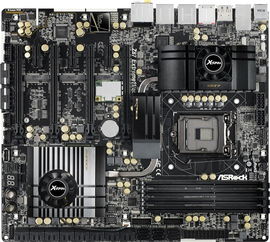

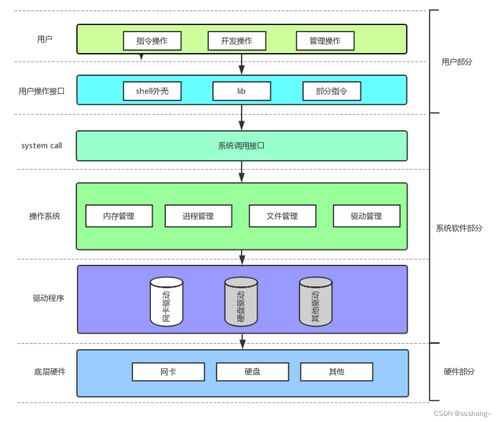

此次發布的計算機軟硬件基礎體系標準由國內權威科研機構、高校和行業領軍企業聯合制定,歷時多年研發和測試。標準全面涵蓋了從處理器、存儲設備、主板等硬件組件,到操作系統、數據庫、中間件等軟件平臺的基礎規范,旨在構建一個統一、兼容、安全的計算環境。該標準不僅明確了軟硬件之間的接口協議和性能指標,還強調了國產化技術的集成應用,為實現技術自主可控奠定了基礎。

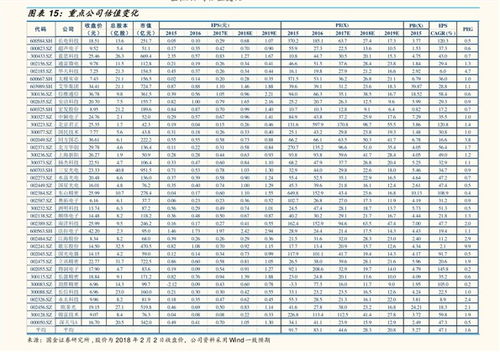

這一標準的推廣預計將大幅降低企業和用戶在軟硬件適配上的成本,同時減少對外部技術的依賴,從而增強我國在全球信息技術競爭中的話語權。隨著標準逐步實施,國內計算機產業鏈有望迎來新一輪發展機遇,尤其在政府、金融、教育等關鍵領域,國產軟硬件的應用將得到進一步普及。

業內專家表示,該標準的發布是我國信息技術標準體系建設的重要突破,未來還需持續完善和迭代,以應對快速變化的技術需求。在全球數字化轉型的浪潮中,這一舉措將助力中國構建更加安全、高效的數字基礎設施,推動數字經濟高質量發展。