模擬集成電路設計 以LDO設計為例(第二版)

隨著電子設備的快速發(fā)展,對高效、穩(wěn)定電源管理芯片的需求日益增長。低壓差線性穩(wěn)壓器(LDO)作為一種關鍵的模擬集成電路,廣泛應用于各類電子系統(tǒng)中,提供穩(wěn)定的電壓輸出。本文以LDO設計為例,探討模擬集成電路設計的核心原理、方法與實踐,并介紹相關資源,如第二版LDO設計講義文檔在CSDN的下載方式。

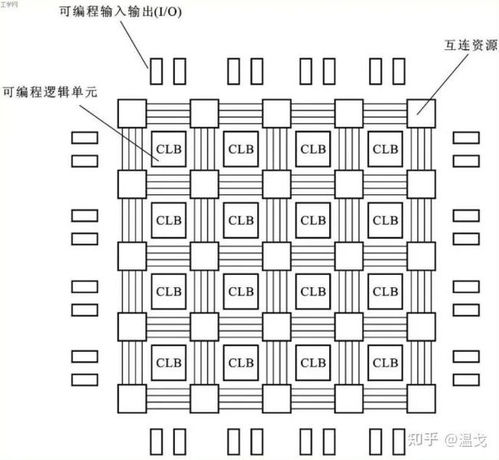

模擬集成電路設計涉及多個關鍵環(huán)節(jié),包括電路架構選擇、晶體管級設計、穩(wěn)定性分析和噪聲優(yōu)化等。LDO作為典型代表,其設計過程充分體現(xiàn)了模擬設計的挑戰(zhàn)與技巧。LDO的核心組件包括誤差放大器、功率晶體管和反饋網(wǎng)絡。設計時需重點關注壓差電壓、負載調(diào)整率、線性調(diào)整率和電源抑制比等性能參數(shù)。例如,壓差電壓決定了LDO在輸入電壓接近輸出電壓時的最小工作電壓,而負載調(diào)整率反映了輸出電流變化時輸出電壓的穩(wěn)定性。

在LDO設計實踐中,穩(wěn)定性是一個常見問題。由于LDO的反饋環(huán)路可能引入相位裕度不足的風險,設計者需采用頻率補償技術,如添加米勒電容或使用緩沖器,以確保系統(tǒng)在各種負載條件下保持穩(wěn)定。噪聲優(yōu)化也至關重要,尤其是在對電源噪聲敏感的應用中,如射頻電路或高精度傳感器。通過選擇低噪聲器件和優(yōu)化布局,可以有效降低LDO的輸出噪聲。

第二版LDO設計講義文檔為學習者和工程師提供了全面指導,涵蓋從基礎理論到高級設計技巧的內(nèi)容。這類資源通常包括設計實例、仿真方法和實際應用案例,幫助讀者深入理解LDO的工作原理。CSDN作為知名的技術社區(qū),提供了此類文檔的下載渠道,用戶可以通過搜索關鍵詞“LDO模擬集成電路設計 講義 第二版”來獲取資源。這些文檔不僅適用于初學者,還能為經(jīng)驗豐富的設計者提供參考。

LDO設計是模擬集成電路領域的經(jīng)典課題,其原理和方法可擴展至其他電源管理電路。通過結(jié)合理論學習和實踐資源,如CSDN上的講義文檔,設計者能夠提升技能,應對日益復雜的電子系統(tǒng)需求。未來,隨著工藝進步和應用多樣化,LDO及其模擬集成電路設計將繼續(xù)演進,推動技術創(chuàng)新。

如若轉(zhuǎn)載,請注明出處:http://www.97club.cn/product/22.html

更新時間:2026-01-27 22:46:36